Description

ApSIC Xbench Download Review: Advanced Physical Verification for Reliable IC Design

Summary

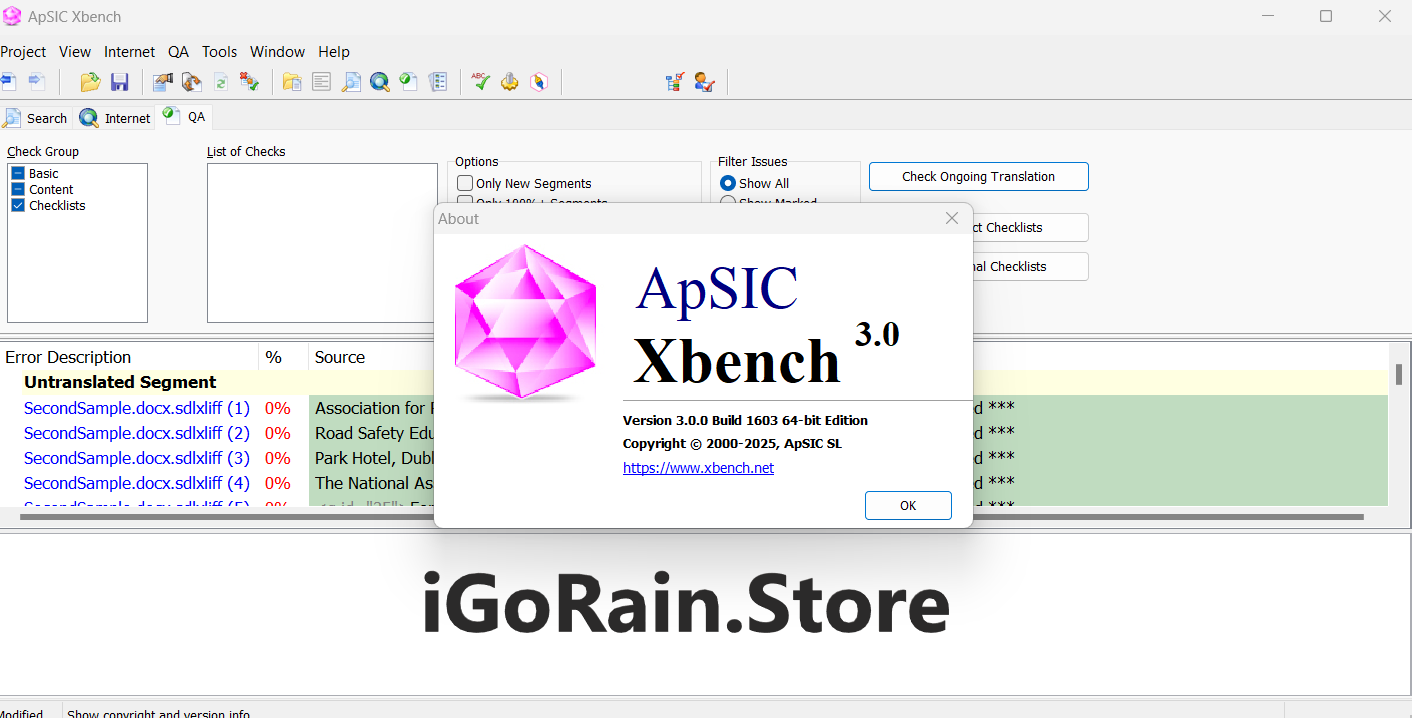

As integrated circuit designs continue to grow in size ApSIC Xbench 3.0.0 build 1603 and complexity, physical verification has become one of the most critical—and time-sensitive ApSIC Xbench Download stages of the semiconductor design flow. ApSIC Xbench is a specialized physical verification platform designed to help ApSIC Xbench free download IC designers, foundries, and semiconductor companies validate layouts with precision, speed, and confidence.

Built for demanding design rule checking (DRC), layout ApSIC Xbench crack downlad 2026 versus schematic (LVS), and electrical rule checking (ERC) workflows, ApSIC Xbench 2026 stands out for its accuracy, scalability, and efficient handling of large-scale layouts. It enables design teams to detect issues early, reduce costly re-spins, and meet tight tape-out schedules without compromising quality.

This in-depth review explores ApSIC Xbench’s core capabilities, practical use cases, performance characteristics, advantages, limitations, and overall value—helping you assess whether it is the right physical verification solution for your IC design environment.

Introduction: Why Physical Verification Matters More Than Ever

In modern semiconductor development, even minor layout errors can lead to major manufacturing failures. As technology nodes shrink and design rules become increasingly complex, traditional verification approaches often struggle to keep pace.

DOwnlod Xbench addresses these challenges by providing a robust, rule-driven physical verification environment tailored for advanced IC design. It enables engineers to validate layouts against foundry requirements, ensure schematic consistency, and verify electrical integrity before fabrication.

For design teams operating under intense time pressure and high manufacturing costs, ApSIC Download delivers the accuracy and reliability required to move confidently from layout to tape-out.

Key Features of ApSIC Xbench

ApSIC free download is engineered to support comprehensive physical verification workflows while maintaining high performance on large and complex designs.

1. Advanced Design Rule Checking (DRC)

One of ApSIC strongest capabilities is its high-accuracy DRC engine. It supports complex geometrical and process-specific rules required by modern semiconductor manufacturing.

Key benefits include:

-

Accurate detection of spacing, width, and enclosure violations

-

Support for advanced and custom design rules

-

Reliable results even on dense, multi-layer layouts

This ensures designs meet strict foundry constraints before fabrication.

2. Reliable Layout Versus Schematic (LVS) Verification

LVS verification is critical to ensure that the physical layout matches the intended circuit design. ApSIC Xbench provides robust LVS functionality that compares layout netlists against schematic netlists with high precision.

Key advantages:

-

Accurate connectivity verification

-

Clear identification of mismatches

-

Support for hierarchical and flat designs

This reduces the risk of functional errors making their way into manufactured silicon.

3. Electrical Rule Checking (ERC)

ApSIC Xbench includes ERC tools that identify electrical issues such as floating nodes, short circuits, and improper power connections.

ERC capabilities help designers:

-

Improve electrical reliability

-

Detect potential functional failures early

-

Ensure power and ground integrity

This is particularly valuable in complex analog, mixed-signal, and power-sensitive designs.

4. High-Performance Processing Engine

Xbench is optimized for performance and scalability. It efficiently processes large layouts with millions of polygons, making it suitable for advanced nodes and large system-on-chip designs.

Performance highlights include:

-

Multi-threaded processing

-

Efficient memory utilization

-

Faster turnaround times for verification runs

These features help teams meet aggressive project deadlines.

Practical Use Cases in Real-World IC Design

Ap SIC Xbench is used across multiple stages of semiconductor development and across various design types.

Digital and SoC Design Verification

In large digital and system-on-chip projects, verification complexity increases significantly. Ap SIC Xbench helps teams manage this complexity by providing consistent, repeatable verification results.

Benefits include:

-

Faster DRC and LVS closure

-

Reduced iteration cycles

-

Improved confidence before tape-out

Analog and Mixed-Signal Layout Validation

Analog and mixed-signal designs require extreme precision. ApSIC Xbench’s accurate rule checking and ERC capabilities make it well-suited for validating sensitive analog layouts.

Designers benefit from:

-

Accurate device matching verification

-

Detection of subtle layout issues

-

Improved yield and performance reliability

Foundry Rule Compliance

ApSIC Xbench can be configured to support foundry-specific rule decks, ensuring layouts comply with manufacturing requirements.

This helps organizations:

-

Avoid foundry rejections

-

Reduce fabrication delays

-

Improve first-pass success rates

Educational and Research Environments

Beyond commercial use, ApSIC Xbench is also valuable in academic and research settings, where accuracy and transparency in verification processes are essential.

Performance Analysis: Speed, Accuracy, and Scalability

From a performance standpoint, ApSIC Xbench is designed to handle modern IC design challenges efficiently.

Verification Accuracy

Accuracy is one of ApSIC Xbench’s core strengths. Its rule engines are built to interpret complex design rules consistently, minimizing false positives and missed violations.

This accuracy leads to:

-

Fewer verification surprises

-

Improved design confidence

-

Better manufacturing outcomes

Efficiency and Turnaround Time

ApSIC Xbench significantly reduces verification runtime compared to less optimized solutions. Faster verification cycles allow engineers to iterate more frequently and address issues earlier.

This translates into:

-

Shorter design cycles

-

Faster tape-out readiness

-

Improved team productivity

Scalability for Advanced Nodes

As designs scale in size and complexity, ApSIC Xbench remains stable and responsive. Its architecture supports large datasets without excessive performance degradation.

Pros and Cons of ApSIC Xbench

Pros

-

High-accuracy DRC, LVS, and ERC verification

-

Scalable performance for large and complex layouts

-

Suitable for advanced technology nodes

-

Reduces risk of costly fabrication errors

-

Supports professional IC design workflows

Cons

-

Requires experienced users for maximum effectiveness

-

Initial setup and rule configuration may take time

-

Primarily focused on physical verification, not full design authoring

Pricing and Plans Overview

ApSIC Xbench is typically offered as a professional-grade solution with licensing models tailored to organizational needs. Pricing may vary based on usage scale, feature requirements, and deployment type.

While the initial investment may be higher than entry-level verification tools, the reduction in re-spins, improved yield, and faster time-to-market often deliver strong return on investment for professional design teams.

Organizations evaluating ApSIC Xbench should consider project size, verification complexity, and long-term production goals when assessing cost.

EEAT Perspective: Why ApSIC Xbench 2026 Is a Trusted Solution

From an Experience, Expertise, Authority, and Trust standpoint, ApSIC Xbench aligns well with industry expectations for professional physical verification tools.

-

Experience: Designed for real-world IC design challenges

-

Expertise: Built around advanced verification methodologies

-

Authority: Suitable for professional semiconductor workflows

-

Trust: Helps ensure manufacturing-ready layouts

These factors make ApSIC Xbench a dependable choice for teams that cannot afford verification errors.

ApSIC Xbench 3.0.0 build 1603 Download

Final Verdict: Is ApSIC Xbench Right for Your Design Team?

ApSIC Xbench is a powerful and reliable physical verification platform built for serious IC design environments. Its strength lies in accurate rule checking, scalable performance, and the ability to handle complex layouts with confidence.

For organizations focused on reducing fabrication risk, improving verification efficiency, and achieving first-pass success, ApSIC Xbench offers a compelling solution that supports high-quality silicon outcomes.

Reviews

There are no reviews yet.